|

用於移動估計的等級C+資料重覆使用架構 用於移動估計的等級C+資料重覆使用架構

|

刊登日期:2014/05/21 |

|

|

|

|

|

| ‧ 專利名稱 |

用於移動估計的等級C+資料重覆使用架構 |

| ‧ 專利證書號 |

I272548

7865026

|

| ‧ 專利權人 |

國立臺灣大學 |

‧ 專利國家

(申請日) |

中華民國 (2005/08/22)

美國 (2005/09/07)

|

|

|

| |

| ‧ 發明人/PI |

陳良基 ,黃朝宗 ,陳慶曄 ,陳翊豪 ,

|

| ‧ 單位 |

電子工程學研究所

|

| ‧ 簡歷/Experience |

|

|

技術摘要 / Our Technology: 技術摘要 / Our Technology: |

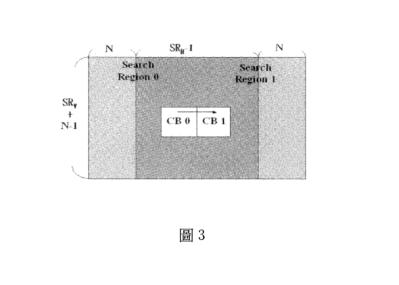

本發明針對區塊比對移動估計(block matching motion estimation)提出了一個高效率的等級C+資料重覆使用架構(data reuse scheme),相對於傳統的等級C(level C)架構,本發明可以在進行移動估計時節省更多的外部圖像記憶體頻寬(external frame memory bandwidth)。其主要精神是針對水平方面的重疊的搜尋區域(searching region)進行資料重覆使用,以及對垂直方向的重疊的搜尋區域進行部份的資料重覆使用,也就是把數個垂直方向連續的目前區塊連接起來,然後同時讀取這幾個目前區塊對應到的搜尋區域。藉著增加小量的內部記憶體容量(internal memory size)來暫存這些讀取進來的搜尋區域,就可以大量的減少外部圖像記憶體頻寬。從對 H.264/AVC的個案研究發現,所提出的等級C+資料重覆使用架構可以在傳統的等級C和D架構之間提供一個不錯的考量(trade-off)。

The present invention provides a scan cell circuit and a scan chain formed by the scan cell circuit, where the scan chain is embedded in a chip for the applications of a test program. The scan cell circuit is formed by two sub-cells connected in serial and each sub-cell includes a multiplexer and a latch. While in the test mode, one of the sub-cells is operating on the positive edge of a clock within a clock cycle and the other sub-cell is operating on the negative edge of the clock. Thus, the scan cell circuit of the present invention can transmit two-bit scan data in each clock cycle and the scan clock frequency can be reduced by a half without having to add any extra test time. The experiment data shows that, in comparison with the conventional Mux-scan technology, the present invention can effectively reduce two third of the power consumption under test mode.

|

專利簡述 / Intellectual Properties: 專利簡述 / Intellectual Properties: |

|

| |

聯繫方式 / Contact: 聯繫方式 / Contact: |

| 臺大產學合作總中心 / Center of Industry-Academia Collaboration, NTU |

|

| Email:ordiac@ntu.edu.tw |

電話/Tel:02-3366-9945 |

|

|

| |

|

| |

|